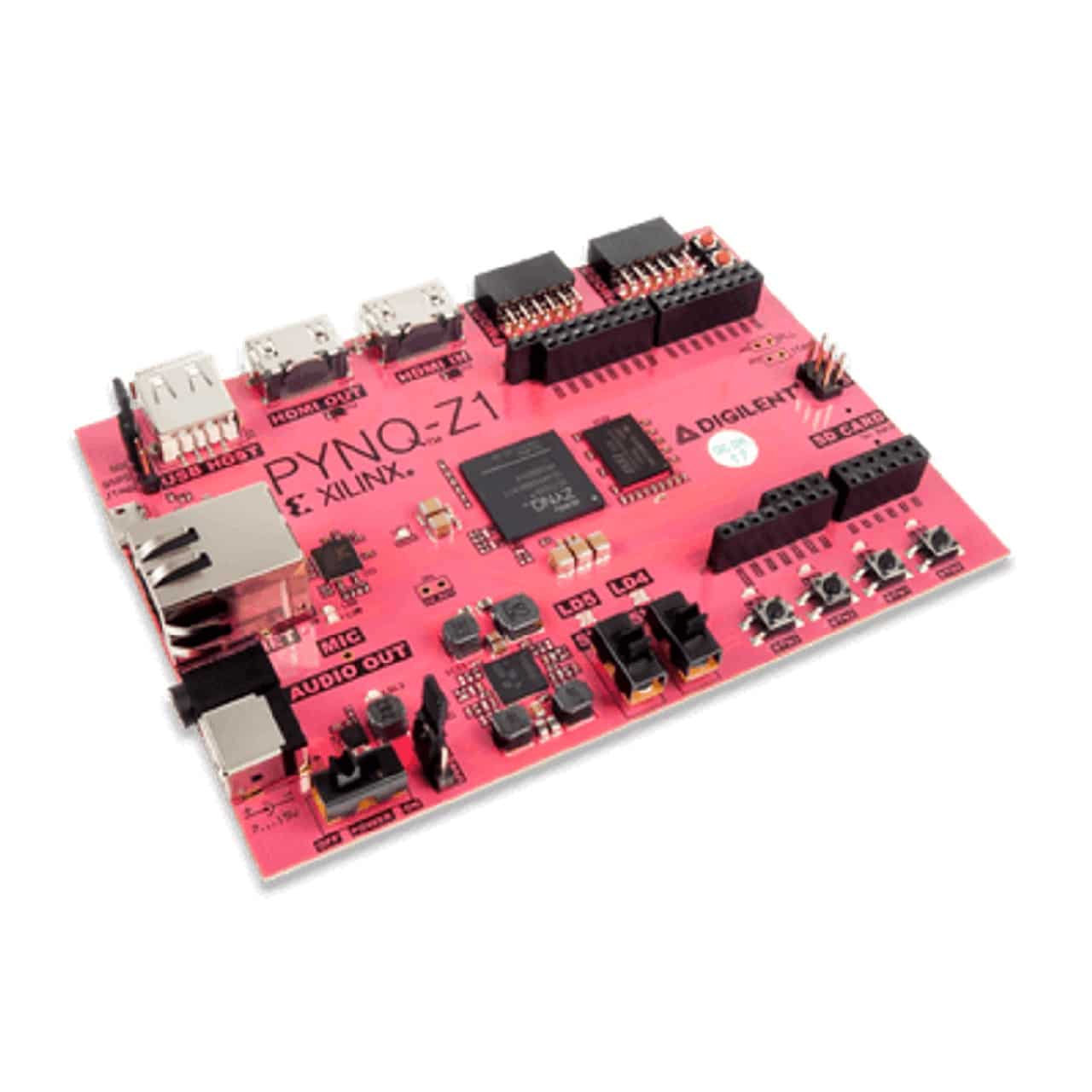

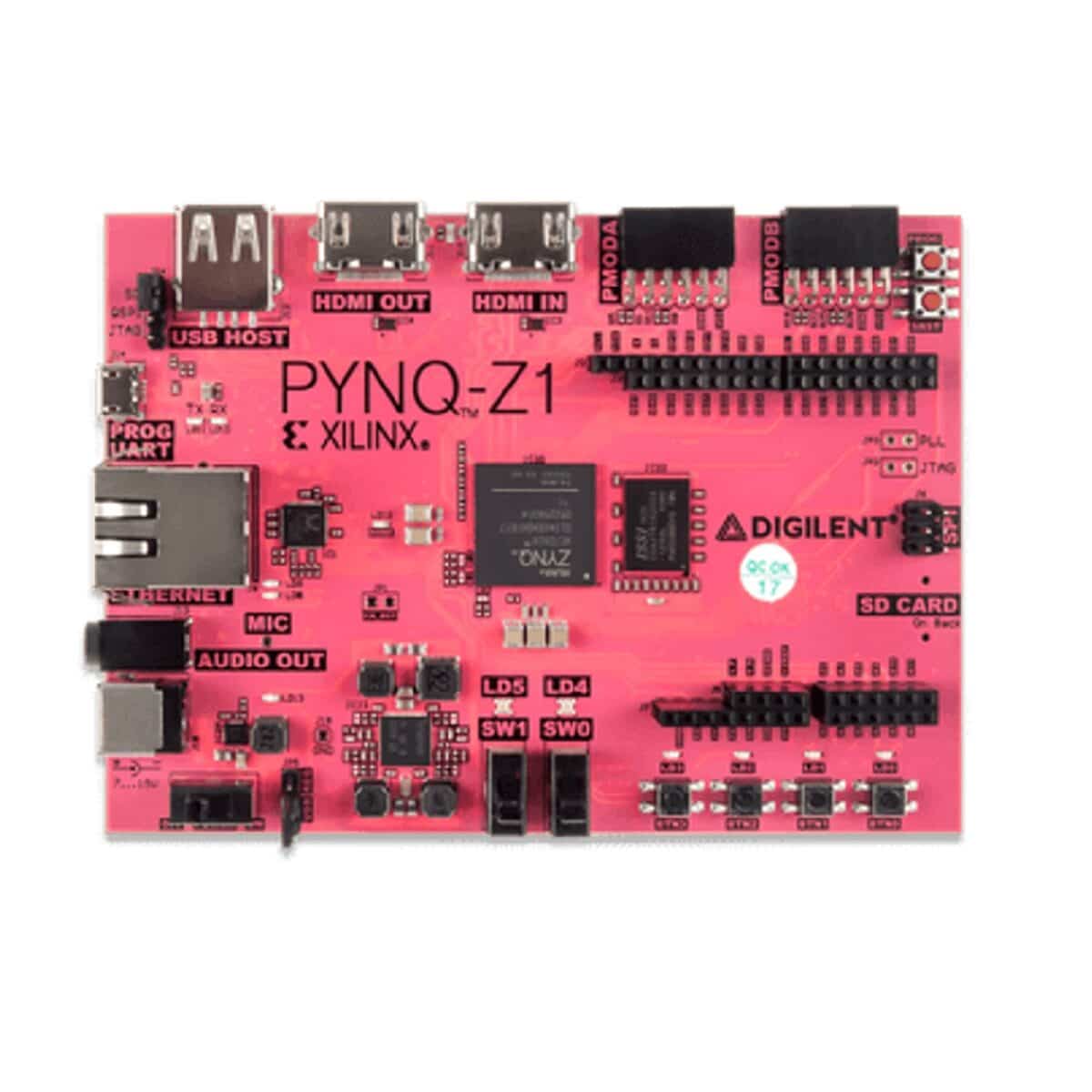

La placa PYNQ-Z1 está diseñada para usarse con el marco de código abierto PYNQ que permite a los programadores integrados programar el SoC integrado con Python. Está diseñado en torno al SoC Xilinx Zynq®-7000, que combina la lógica programable de un FPGA con un procesador ARM Cortex™-A9 de doble núcleo.

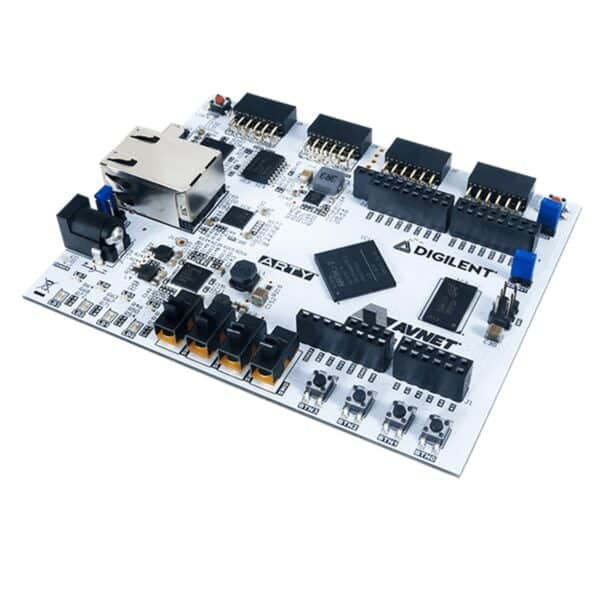

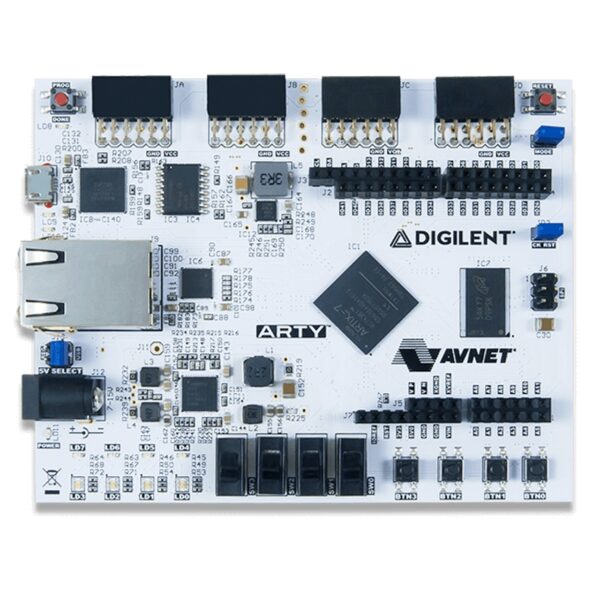

En cuanto al hardware, el PYNQ-Z1 es flexible y está listo para usar. Es similar en factor de forma y características al Arty Z7 de Digilent, con encabezados Arduino™ populares, puertos Pmod, E/S integradas, entrada/salida HDMI, salida de audio y conectividad USB y Ethernet. Esto convierte al PYNQ-Z1 en una plataforma de desarrollo de SoC versátil y fácilmente personalizable para aplicaciones tales como visión artificial, control industrial, IoT, cifrado y aceleración informática integrada.

Lo que realmente distingue al PYNQ-Z1 es el marco de código abierto de PYNQ. (Consulte la pestaña Software para obtener más detalles sobre el marco PYNQ). La placa se puede iniciar desde una tarjeta microSD que contenga la imagen de inicio PYNQ-Z1. La imagen PYNQ-Z1 se puede descargar gratis y copiar a una tarjeta microSD

Para los diseñadores que desean ampliar el sistema base mediante la contribución de nuevas bibliotecas de hardware, las herramientas de edición Xilinx Vivado Design Suite WebPACK están disponibles sin costo alguno.

Caracteristicas

- ZYNQ XC7Z020-1CLG400C

- Procesador Cortex-A9 de doble núcleo a 650 MHz

- Controlador de memoria DDR3 con 8 canales DMA y 4 puertos esclavos AXI3 de alto rendimiento

- Controladores de periféricos de gran ancho de banda: 1G Ethernet, USB 2.0, SDIO

- Controlador periférico de bajo ancho de banda: SPI, UART, CAN, I2C

- Programable desde JTAG, Quad-SPI flash y tarjeta microSD

-Lógica programable equivalente a Artix-7 FPGA

-13 300 segmentos lógicos, cada uno con cuatro LUT de 6 entradas y 8 flip-flops

-630 KB de RAM de bloque rápido

-4 mosaicos de administración de reloj, cada uno con un bucle de bloqueo de fase (PLL) y un administrador de reloj de modo mixto (MMCM)

-220 cortes DSP

-Convertidor de analógico a digital en chip (XADC) - DDR3 de 512 MB con bus de 16 bits a 1050 Mbps

- Flash Quad-SPI de 16 MB con identificador único global programado de fábrica (compatible con EUI-48/64™ de 48 bits).

- Ranura MicroSD

- Alimentado desde USB o cualquier fuente de 7V-15V

- USB y Ethernet:

- Circuito de programación USB-JTAG

- Puente USB-UART

- USB OTG PHY (solo admite host)

- Gigabit Ethernet PHY

- Micrófono electret con salida modulada por densidad de pulso (PDM)

- Conector de salida de audio mono de 3,5 mm, formato modulado por ancho de pulso (PWM)

- Puerto disipador HDMI (entrada)

- Puerto de fuente HDMI (salida)

- 4 pulsadores

- 2 interruptores deslizantes

- 4 LED

- 2 LED RGB

- Dos puertos Pmod estándar

- 16 E/S de FPGA totales

- Conector de escudo Arduino/chipKIT

- 49 E/S total de FPGA

- 6 entradas analógicas de 0-3,3 V de un solo extremo a XADC

- 4 entradas analógicas diferenciales de 0-1,0 V a XADC

- HTC: 8471500150

- ECCN: 5A992.c